Author:

H. Rahman

March 28, 2023

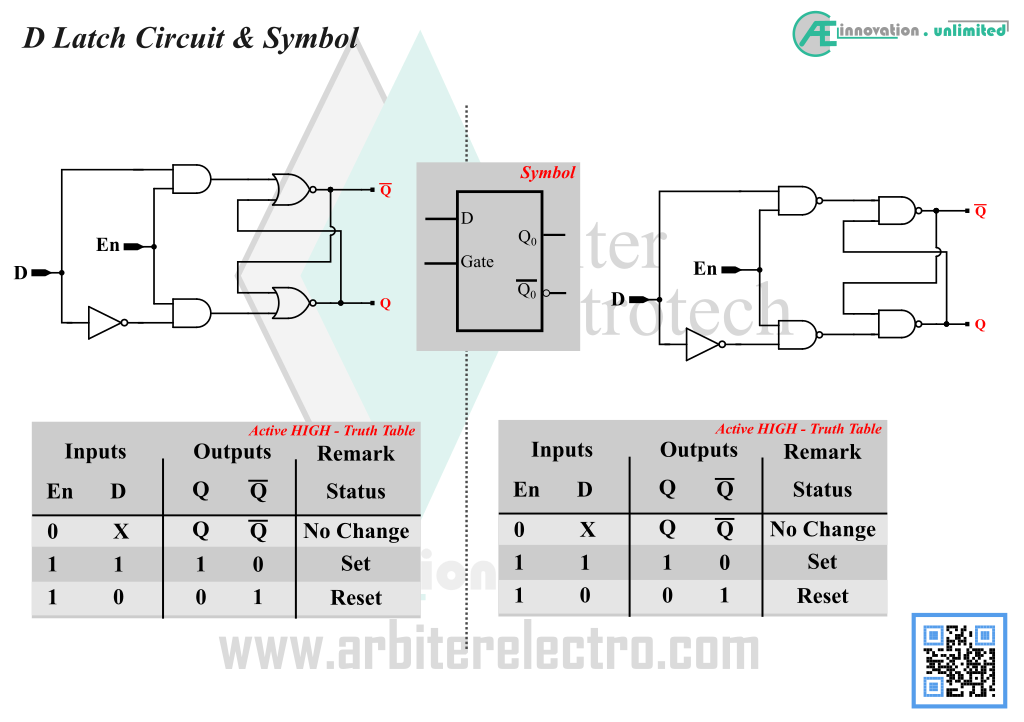

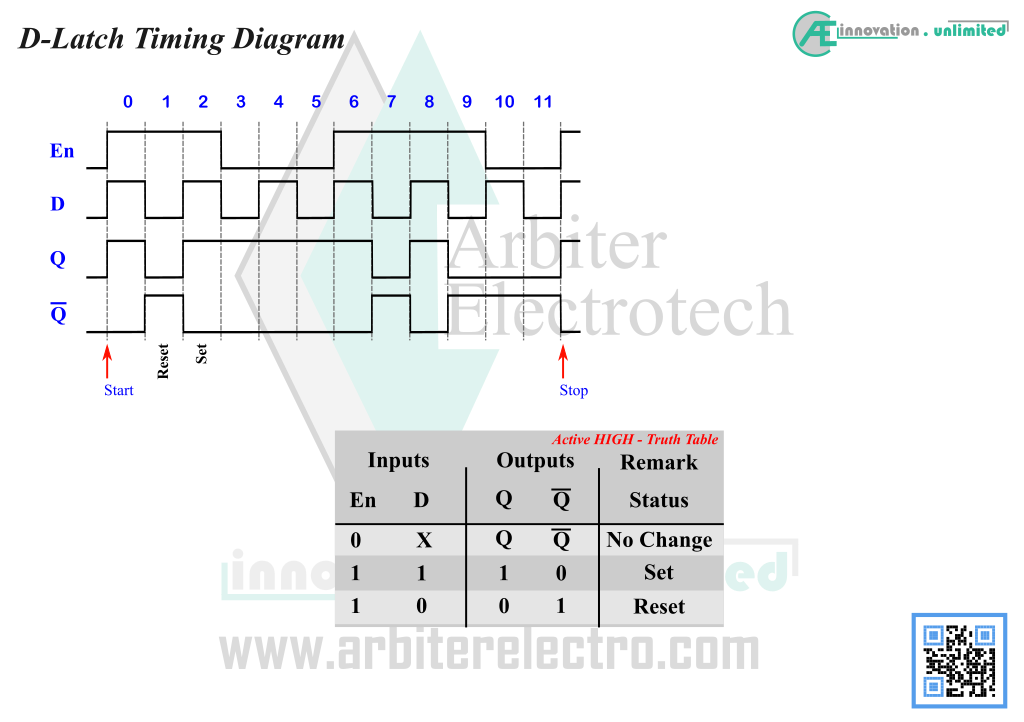

A “D latch” or “Data Latch” is an improved version of SR latch and Gated SR latch. The improved properties are due to the fact that a Data latch has no invalid state like the other aforementioned latches. The absence of invalid state is due to the design of the latch. The circuit/schematic of a D latch is shown below. First point to notice is that there are only one input data input. Other latches had 2 data inputs (S & R). Secondly, one of the data input of the gates comes through a NOT gate. This configuration makes sure that both of the input of a D latch is never 1 or 0 at the same time. The inputs S and R of the D latch are always either 1-0 or 0-1. As the inputs cannot be 1-1 or 0-0, this means that the D latch will never encounter the invalid state.

A Gated SR latch is used to implement the D latch. It has all the advantages of a Gated SR latch but no invalid state. The input EN/GATE is to control the flow of data (just like the Gated SR latch). It enables/disables the data input from reaching the latch input.

Leave a Reply